# Rob A. Rutenbar 2017 ESDA/CEDA Phil Kaufman Award

Award Presenter: Martin D.F. Wong Univ. of Illinois at Urbana-Champaign

# An Appreciation, in Three Acts ...

The ideas

The impact

The individual

# An Appreciation, in Three Acts ...

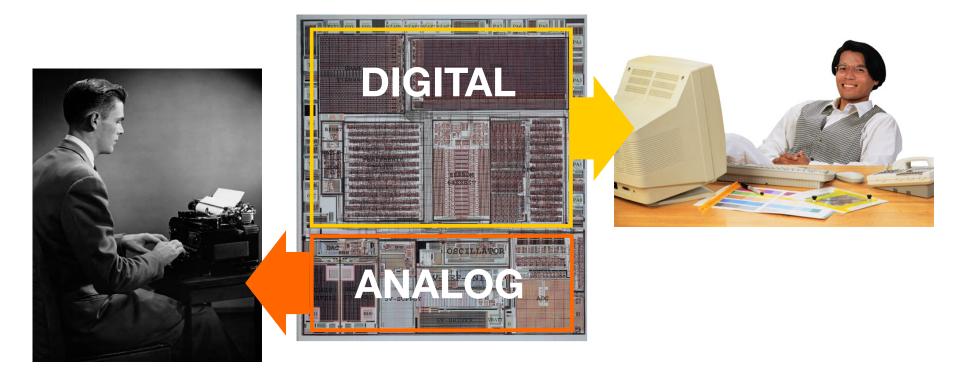

# Some History: In the 1980s...

- It became possible for students & faculty to do chips

- This was the VLSI revolution, and Rob was there

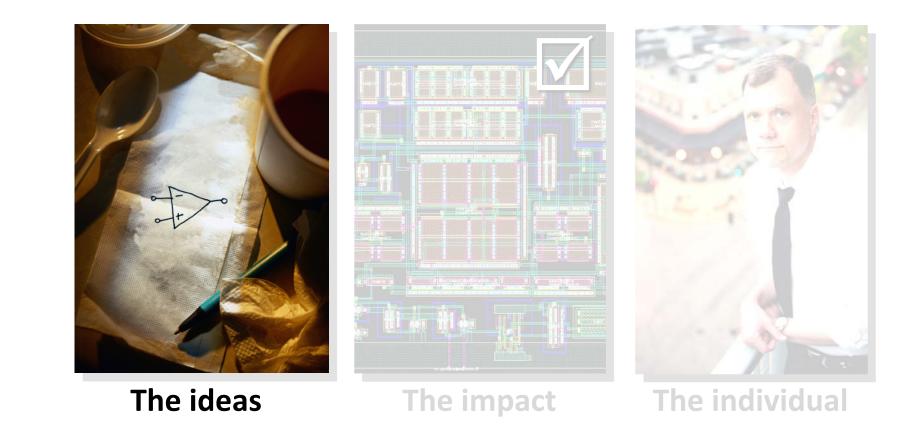

# 80s and 90s $\rightarrow$ Digital ASIC Flows

- Big ideas in synthesis

- Big ideas in verification

- Big ideas in logic

- Big ideas in layout

- Big ideas in timing

- And flows, flows, FLOWS...

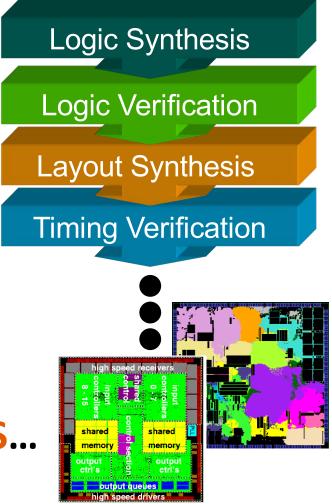

# Just One Little Problem...

# Analog CAD Was Not Happening

Aside from core simulation tech (SPICE-ish), EDA was a vast, empty wasteland for non-digital designs

# Some Kaufman-Centric History...

### A strong tradition of awards to those simulation pioneers

# But Rob Saw a Large Opportunity

## ...which he spent the next 20+ years working on as faculty at Carnegie Mellon

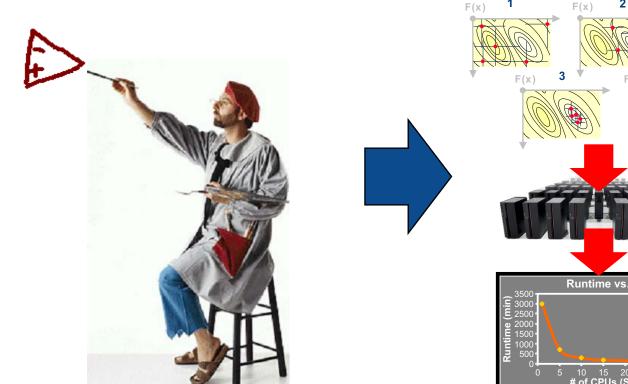

# Rob's Big Idea

Analog – it's art, it's deep, mysterious, painful, sublime...

# NO – it's optimization. Big hard optimization.

# Rob's Big Idea, Revisited

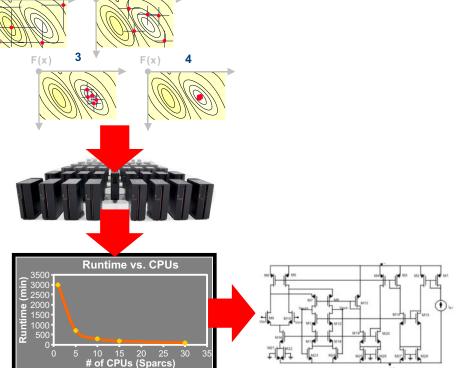

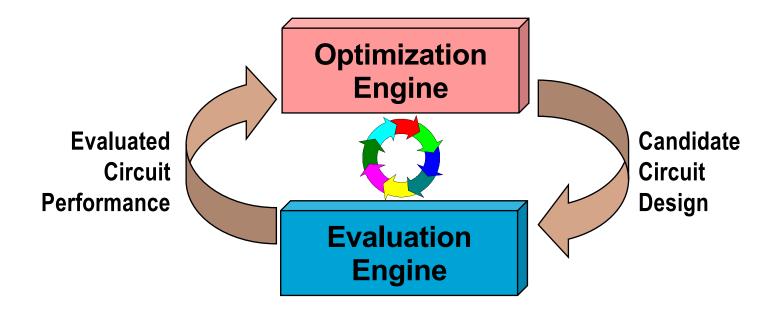

Clever models & engines can support principled search for best analog design to meet designer constraints

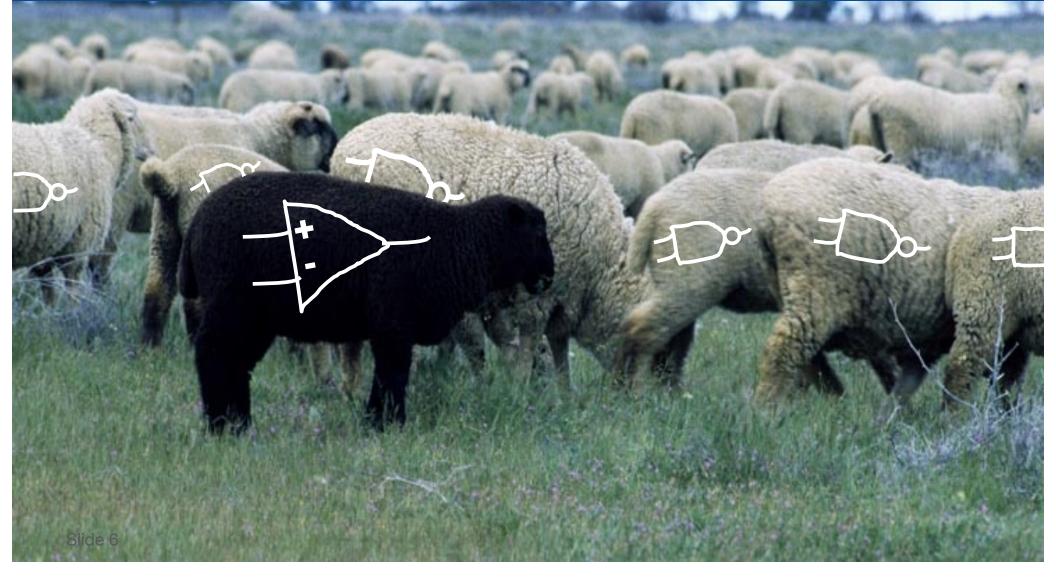

# Pursued Across Breadth of Analog

**OPTIMIZATION SIZING** LAYOUT 2.4 SPICE 403 dimensions -0.14 Full 64b SRAM col Model -0.15 -0.16 90th percentile (FO4) 5°2 2°2 -0.17 **QMC** -0.18 Pseudo Random 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 2.25<sup>L</sup> Time x  $10^{-7}$ 20 40 60 80 100 100s of points MACROMODELING **STATISTICS**

Slide 12

0.5

0.3

0.2

0.1 0.0 -0.1 -0.2 -0.3 -0.4

-0.5 0

Vout 0.4

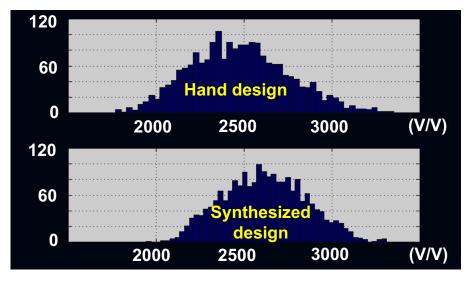

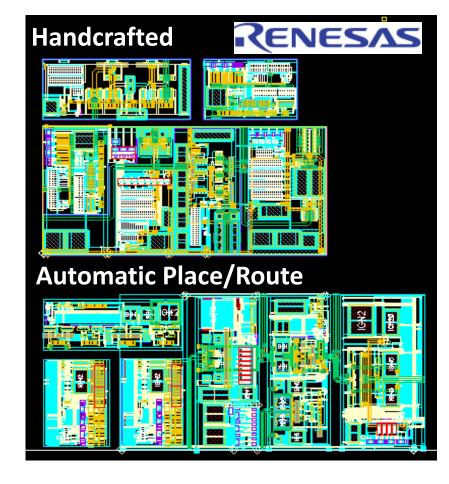

# Two Analog Examples

Practical Spice-in-the-Loop optimizers that "just work"

### Automatic layouts with manual aesthetics & performance

# An Appreciation, in Three Acts ...

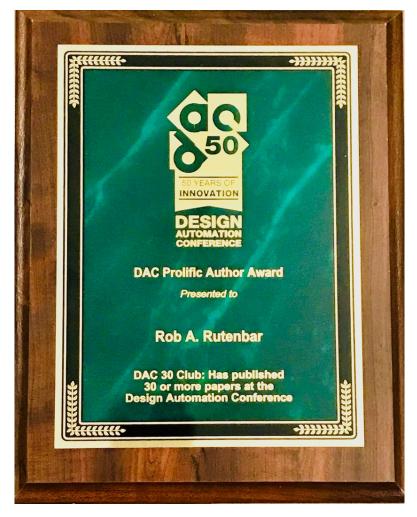

# Academic Impact (Of Course)

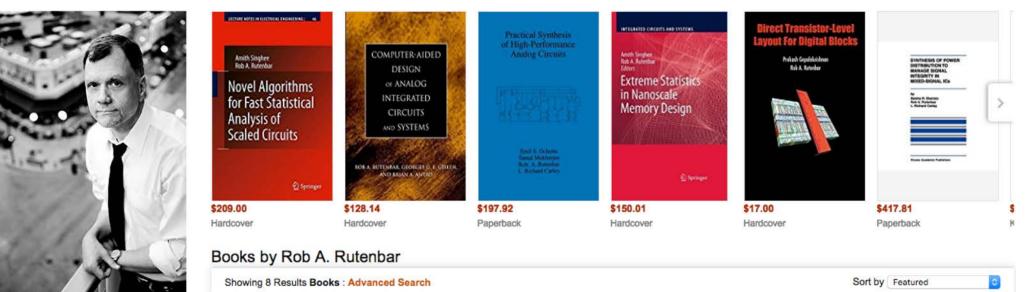

- 200+ papers, books etc

- ~10,000 citations

- Many, many awards

- Best Papers

- IEEE TCAD Pedersen Awards

- DATE Best Paper

- ICVLSI Best Paper

### Rob A. Rutenbar

+ Follow

All Formats Kindle Edition Paperback Hardcover

# Contributed to EDA & Tech Community

# More Critically – Deep Industry Impact

Rob A. Rutenbar Chief Technologist

Neo Linear, Inc. 311 South Craig Street Suite 102 Pittsburgh, PA 15213 Tel 412.681.1080 FAX 412.681.0802

rutenbar@neolinear.com

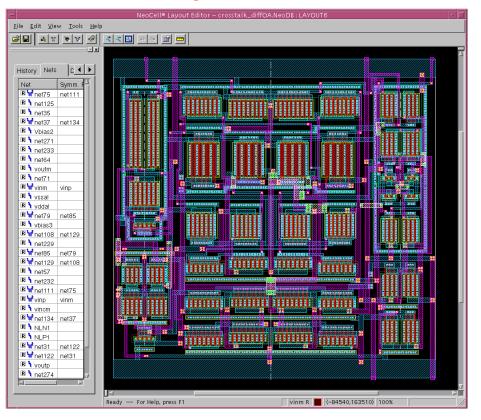

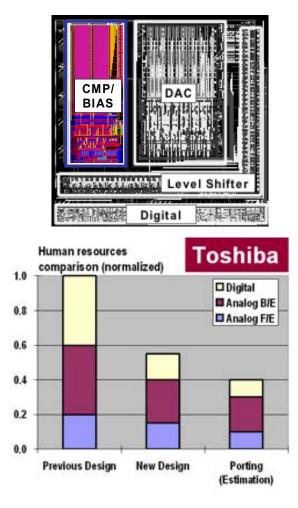

# Neolinear: Front-to-Back Analog Tools

# **Neolinear: Customers**

### NeoCircuit & NeoCircuit-RF ELPIDA The Power of Focus ACCEN SAMSUNG Elpida Memory, Inc. SANYO **Matsushita** Toshiba U TEXAS INSTRUMENTS **DNPsemi**conductor Infineon technologies DNP半導体製品事業部 **CISCO SYSTEMS** DAN GIII ահիստումիս Ø BOEING AMI SEMICONDUCTOR NEC SONY

# 2004: Neolinear $\rightarrow$ Cadence

Get

Financial News

Press Release

Enter symbol(s)

Source: Cadence Design Systems, Inc.

Basic

### Cadence to Acquire Neolinear

Tuesday April 6, 8:30 am ET

Neolinear Technology to Accelerate Design Cycle and Enhance Silicon Yield

SAN JOSE, Calif.--(BUSINESS WIRE)--April 6, 2004--Cadence Design Systems, Inc. (NYSE:<u>CDN</u> - <u>News</u>) today announced it plans to acquire Neolinear, Inc., a privately held company. Neolinear's rapid analog design technology is critical for the consumer and communications markets where semiconductors are increasingly differentiated by their analog content. The Neolinear team will bring additional strong A/MS and RF expertise into Cadence and play a key role in driving ongoing innovations for improving yield and speeding IP reuse in the Cadence® Virtuoso® custom design platform. Neolinear's NeoCircuit and NeoCell are already an extended part of the industry-leading Virtuoso platform through an OEM agreement between the two companies.

# Now: Cadence Pittsburgh

# But Also Another Impact: Teaching

- Rob is an extraordinary, dedicated teacher

- His CMU class alums are a Who's-Who of EDA leaders

# Won Major Teaching Awards

# Like: SRC Aristotle Award

Acknowledges impact of Rob's students on US semiconductor industry

# Another Measure of Impact

### What happens when you type this...?

| VLSI CAD |        |        |      |      |          | Q     |

|----------|--------|--------|------|------|----------|-------|

| All      | Images | Videos | News | Maps | Settings | Tools |

# Answer: You Get **Rob** (8 of Top 10!)

About 341,000 results (0.39 seconds)

#### VLSI CAD Part I: Logic | Coursera https://www.coursera.org/learn/vlsi-cad-logic \*

About this course: A modern VLSI chip has a zillion parts -- logic, control, memory, interconnect, etc. How do we design these complex chips? Answer: CAD software tools. Learn how to build thesA modern VLSI chip is a remarkably complex beast: billions of transistors, millions of logic gates deployed for computation and ...

#### VLSI CAD Part II: Layout | Coursera

#### https://www.coursera.org/learn/vlsi-cad-lavout -

About this course: You should complete the VLSI CAD Part I: Logic course before beginning this course. A modern VLSI chip is a remarkably complex beast: billions of transistors, millions of logic gates deployed for computation and control, big blocks of memory, embedded blocks of pre-designed functions designed by third ...

# #3 Bootleg of Rob's MOOC

#1 Rob's MOOC -

#2 Rob's MOOC -

# #4 *Review* of Rob's MOOC

#### VLSI CAD: Logic to Layout Lecture 001 Welcome and Introduction ...

#### Mar 11, 2013 - Uploaded by Alireza Saberi Alireza Saberi. ... Course is presented by professor Rob A. Rutenbar is the Abel Bliss Professor and ...

#### Reviews for VLSI CAD Part I: Logic from Coursera | Class Central https://www.class-central.com > Coursera \*

\*\*\*\* Rating: 5 - 3 reviews

A modern VLSI chip has a zillion parts -- logic, control, memory, interconnect, etc. How do we design these complex chips? Answer: CAD software tools. Learn how to build thesA modern VLSI chip is a remarkably complex beast: billions of transistors, millions of logic gates deployed for computation and control, big blocks of ...

# Reminder: Massive Open Online Courses

### Internet-scale video (for instruction)

### Cloud-based assignments (for eval & grading)

## In 2013, Rob Launched First EDA MOOC

## And, its been running ever since, including right now...

COURSERCI | Global Partners

Courses Partners About - | Sign In Sign Up

### ILLINOIS

### **VLSI CAD: Logic to Layout**

#### Rob A. Rutenbar

A modern VLSI chip has a zillion parts -- logic, control, memory, interconnect, etc. How do we design these complex chips? Answer: CAD software tools. Learn how to build these tools in this class.

Workload: 10-12 hours/week

# **EDA MOOC Impact**

It is estimated there are roughly 25,000 EDA professionals on the planet

Rob's MOOCs, since 2013, have enrolled 64,310 of them **~100 more every week**

# An Appreciation, in Three Acts ...

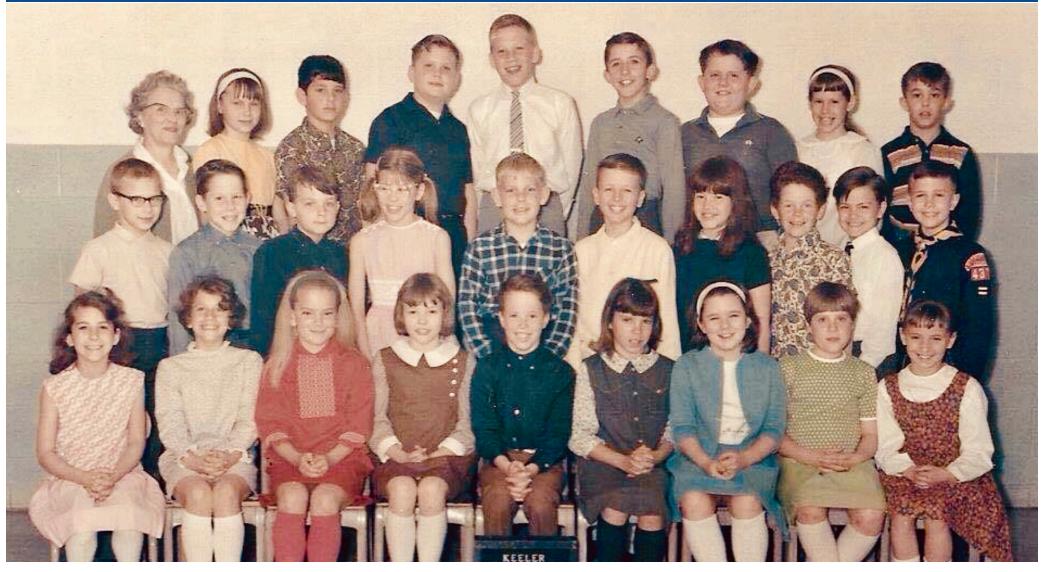

# Just Another Kid from Detroit...

# Rob: Five Schools, Forty Years

**'84-'09 CMU (Faculty) Carnegie Mellon University**

'10-'17 UIUC (Head)

'17-now Pitt (VC Research)

University of Pittsburgh

# Prof. Rutenbar $\rightarrow$ Manager/Boss

### Head of CS at University of Illinois at Urbana-Champaign

### Vice Chancellor for Research at University of Pittsburgh

# New Friends, New Challenges

# Rob's Key Nontechnical Achievements

# Rob Rutenbar: 2017 Kaufman Award

Congratulations to Rob, our friend & colleague, for his lifetime of contributions to EDA